PCB Design Power Ground Plane Overlap Rule

Wiring is an important part of PCB design, and it is also the largest and most time-consuming part of the entire PCB design. When conducting PCB layout work, engineers need to follow some basic rules, such as chamfering rules, 3W rules, etc.

Ground loop rules

The minimum rule of the loop is that the area of the loop formed by the signal line and its loop should be as small as possible. The smaller the loop area, the less external radiation and the smaller the interference received from the outside world. In response to this rule, when dividing the ground plane, the distribution of the ground plane and important signal traces must be considered to prevent the problems caused by the slotting of the ground plane; in the double-layer board design, in the case of leaving enough space for the power supply, the remaining part should be filled with reference ground, and some necessary ground vias should be added to effectively connect the double-sided ground signals, and try to use ground isolation for some key signals. For some designs with higher frequency, special consideration should be given to the ground signal loop problem. It is recommended to use a multi-layer board.

Shield protection rules

Corresponding to the ground loop rule. In fact, it is also to minimize the loop area of the signal. It is more common in some more important signals, such as clock signals and synchronization signals. For some particularly important signals with particularly high frequencies, copper shaft cables should be considered. Shielding structure design, that is, The lines to be distributed are isolated from the ground, the left, the right, and the ground, and it is necessary to consider how to effectively combine the shielded ground with the actual ground plane.

Crosstalk control rules

Crosstalk refers to the mutual interference caused by long parallel wiring between different networks on the PCB, mainly due to the distributed capacitance and distributed inductance between the parallel lines. The main measures to overcome crosstalk are:

Increase the spacing of parallel wiring and follow the 3W rule;

Insert a grounded isolation line between parallel lines;

Reduce the distance between the wiring layer and the ground plane.

3W rule

In order to reduce crosstalk between lines, the line spacing should be sufficiently large. When the line center spacing is not less than 3 times of the line width, 70% of the electric field can be kept from interfering with each other. This is called the 3W rule. If you want to achieve 98% of the electric field does not interfere with each other, you can use a 10W spacing.

Route control rules

The routing direction control rule is that the routing directions of adjacent layers form an orthogonal structure. Avoid putting different signal lines in the same direction on adjacent layers to reduce unnecessary interlayer interference; when the board structure is limited (such as some backplanes), it is difficult to avoid this situation, especially when the signal rate is high. It should be considered to isolate each wiring layer with a ground plane and isolate each signal line with a ground signal line.

Open loop inspection rules for alignment

It is generally not allowed to have a floating wire at one end (Dangling Line), mainly to avoid the "antenna effect" and reduce unnecessary interference radiation and acceptance, otherwise it may bring unpredictable results.

Route closed loop inspection rules

Prevent signal lines from forming self-loops between different layers. Such problems are prone to occur in the design of multilayer boards, and self-loops will cause radiated interference.

Chamfer rule

PCB design should avoid sharp and right angles as they will casue unnecessary radiation and poor process performance.

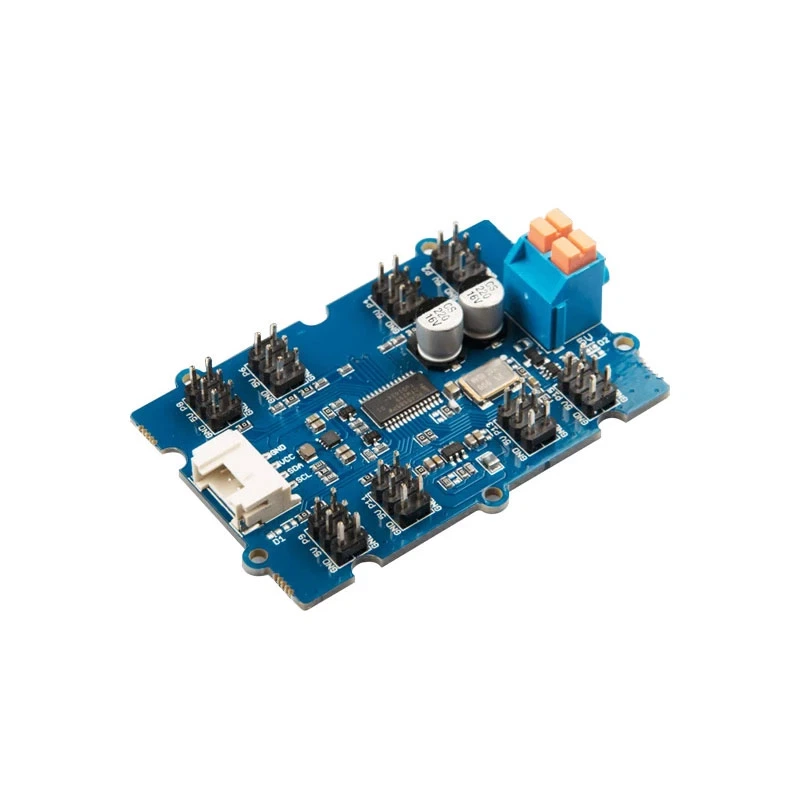

Device decoupling rules

Add the necessary decoupling capacitors on the printed plate to filter out the interference signal on the power supply and make the power supply signal stable. It is recommended that the power supply be connected to the power supply pin after the filter capacitor.

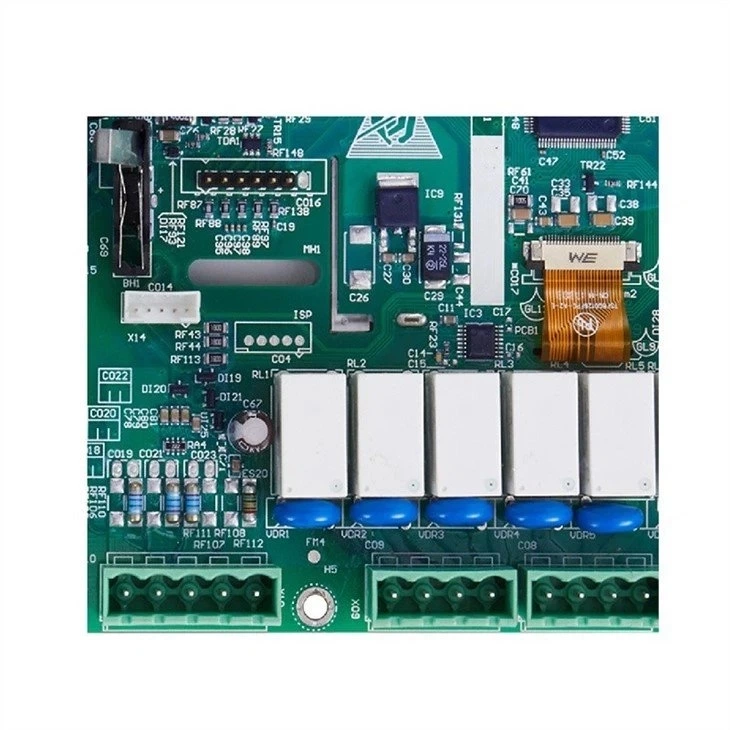

Power ground plane integrity rules

For areas with dense vias, care should be taken to avoid the interconnection of holes in the hollowed-out area of the power supply and the ground layer, which forms a division of the planar layer, thereby destroying the integrity of the planar layer, and thereby causing the loop area of the signal line in the ground layer to increase . In order to avoid destroying the plane layer, the via spacing should at least ensure that one signal line can be used when doing Fanout.

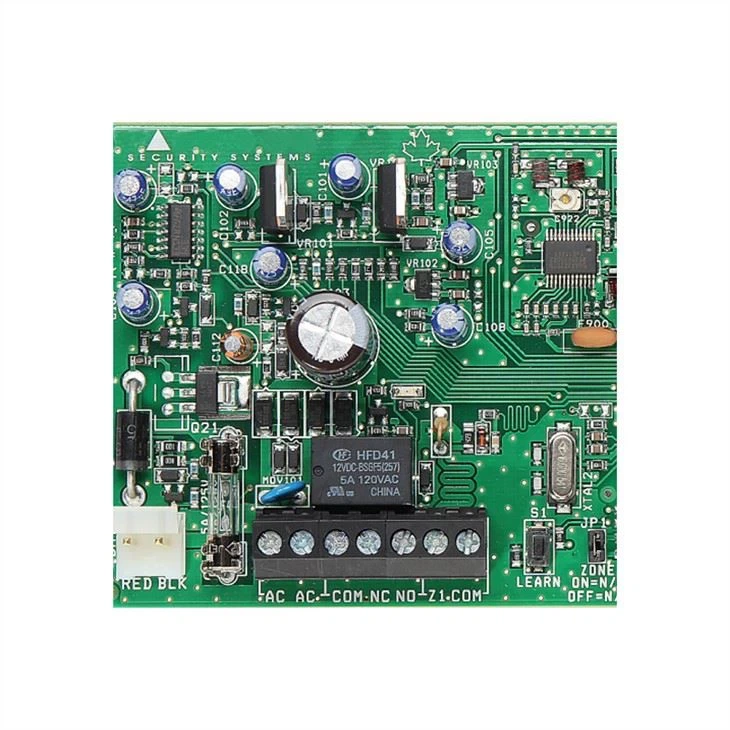

Power ground plane overlap rule

Different power layers should avoid overlapping in space. The main purpose is to reduce the interference between different power supplies, especially between power supplies with very different voltages. The overlapping of power planes must be avoided. When it is difficult to avoid, you can consider the middle interval formation.

20H rule

Since the electric field between the power layer and the ground layer is changing, electromagnetic interference will be radiated outwards at the edge of the board. This is called the edge effect. The solution is to shrink the power layer so that the electric field is conducted only within the range of the ground layer. Taking one H (medium thickness between power supply and ground) as the unit, if shrinking 20H can limit 70% of the electric field to the edge of the ground layer; shrinking 100H can limit 98% of the electric field.